热点内容

浏览量

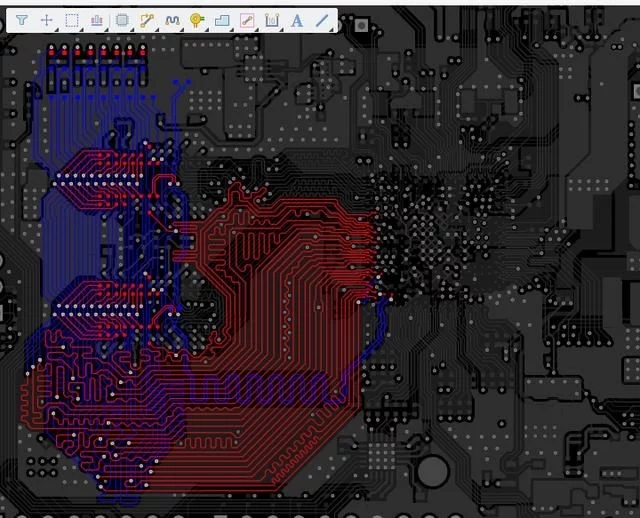

PCB设计:规划良好的信号返回路径

2018-04-02来源:百能网638

PCB设计中有一个"信号返回路径"的概念,理解这一概念对做好PCB设计非常重要。有关"信号返回路径"的详细论述就不在这里赘述了,有兴趣的朋友可以查阅相关资料,比如于博士的SI设计手记。

高速PCB设计

一个不良的信号返回路径是造成噪声耦合和EMI问题的重要原因。因此,在PCB走线的时候需要时刻考虑信号电流的返回路径。当然,电源线和低速信号只需做到尽量短即可(减小电阻)。高速的信号在布线时需保证信号线下方的铜皮不发生割裂的情况。

信号的返回路径

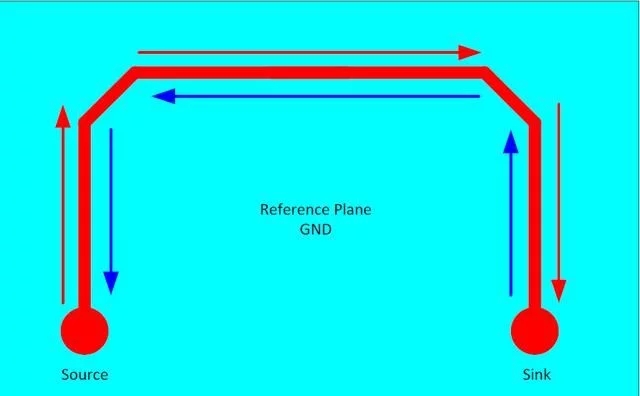

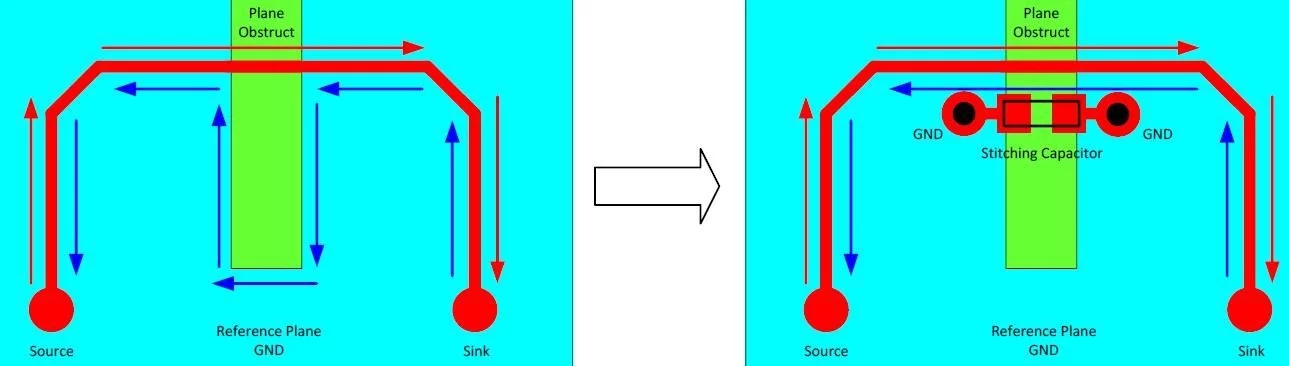

信号返回电流需要跟随PCB走线的轨迹,因此高速信号线不可以跨越电源平面分割处。如果信号电流路径和返回电流的路径不能重合,那么两个路径之间的区域将成为一个环形天线,会造成严重的EMI、SI问题。在不可避免的情况下,有一个电源平面必须在信号的源端和末端之间分割,那么为了良好的返回路径,我们需要沿着分割出来的电源平面的边界走线,而不是直接跨过去,如下图所示。

绕过平面割裂处

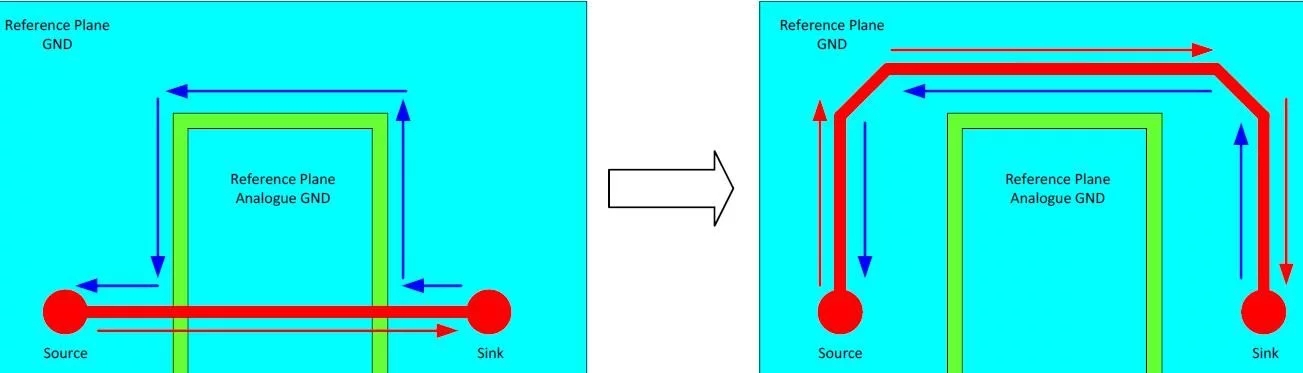

考虑另一种情况,假设信号源端和信号的末端分别在两个电源平面上,那我们就没有办法像上面那样沿着平面的边界走线。这时候就要请出一位"重要角色"了。我们知道电容具有阻直流、通交流的特性,所以当出现上述情况的时候可以在两个电源平面之间跨接一个小电容,这就让返回电流有一个路径可以通过,此电容外号"缝合电容",英文名" stitching capacitor"。缝合电容需要放在信号线跨分割位置附近,越近越好。电容的容值通常在10nF到100nF之间,具体的数值还需要仿真或者实际调试决定。另外,这个电容由于比较特殊,最好选用低ESR值的小封装贴片电容。

放置缝合电容

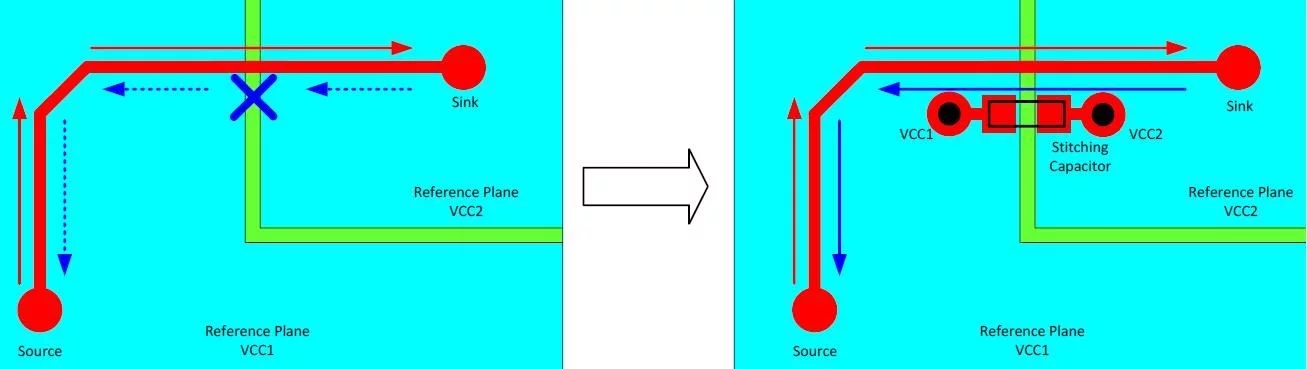

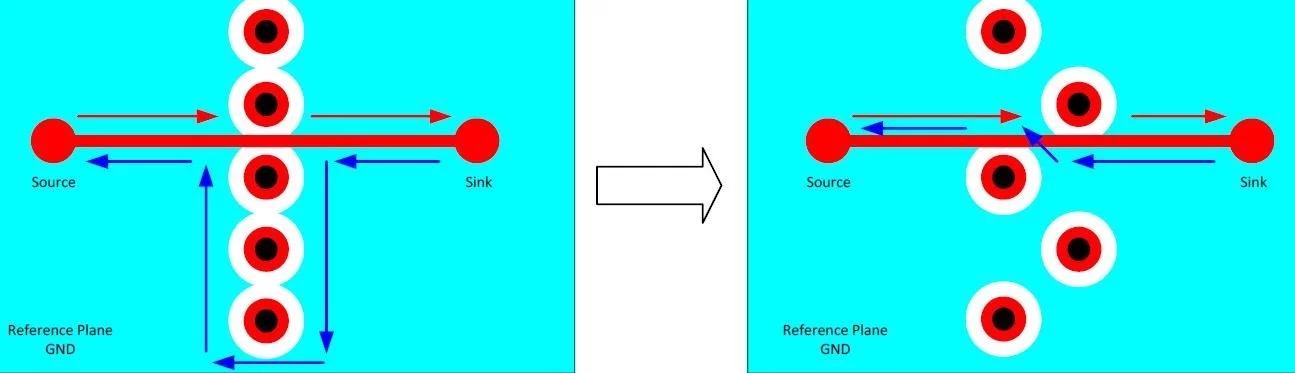

在一些需要存在电源平面挖空的情况下,为了避免信号完整性问题就需要围绕着掏空区域的边界走线,在不可避免要跨越挖空区域的时候,也同样需要添加缝合电容。

挖空处跨接缝合电容

针对SMD类型的器件进行扇孔时有些工程师喜欢将所有的信号过孔排列成整齐的一字形。但是这样的做法常常会引起一系列的问题。首先,当器件管脚的间距比较小时,过孔的间距也是很小的。这就很容易因为过孔挨得太近造成电源平面的割裂。平面割裂影响了平面完整性导致平面的实际过电流的宽度减小,即使没有割裂但是两个过孔之间的电源平面通道非常狭窄也会导致电流密度过大,造成PI问题,更严重的是,当信号线从这两个过孔中间穿过时由于下方已经割裂,实际上信号线已经跨分割了。其次,过孔距离太近可能使两个过孔之间没有足够的空间可以过一根线,这样一排 过孔实际上已经挡住了很大的布线空间。另外,两个孔之间的距离太近也会对PCB的生产制造造成问题,这也是高版本Altium Designer里面加入Hole to hole 规则的原因。为了规避这些问题,我们可以错开打孔。这样的好处是可以使这些过孔之间可以穿过更多的线,而且不会造成平面割裂。

错开过孔提高信号质量

IC类

IC类 二三极管

二三极管 阻容感

阻容感 连接器

连接器 传感器

传感器 机电产品

机电产品 PCB

PCB 无线线圈

无线线圈